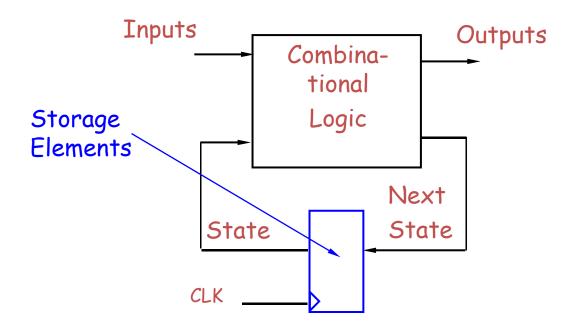

### Sequential Synchronous Circuit Analysis

#### ✓ General Model

- Current State at time (t) is stored in an array of flip-flops.

- Next State at time (t+1) is a Boolean function of State and Inputs.

- Outputs at time (t) are a Boolean function of State(t) and (Mealy) of Inputs (t).

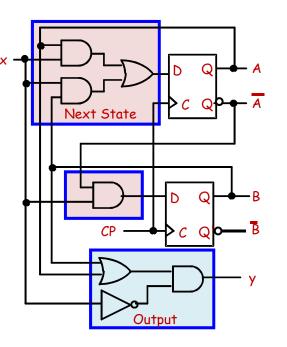

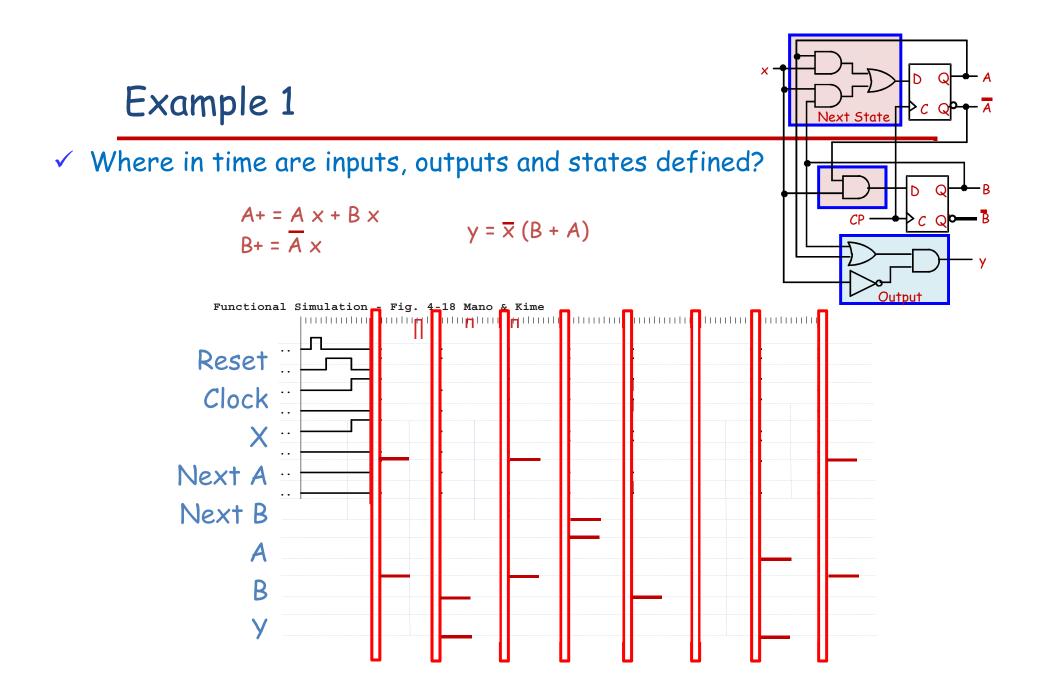

### Example 1: Analysis

- ✓ Input: x(t)

- ✓ Output: y(t)

- ✓ State: (A(t), B(t))

- ✓ What is the Output Function?

$\gamma(\dagger) = \overline{x}(\dagger)(B(\dagger) + A(\dagger))$

✓ What is the Next State Function?

A(++1) = A(+)x(+) + B(+)x(+)B(++1) =  $\overline{A}(+)x(+)$

#### State Table Characteristics

- State table a multiple variable table with the following four sections:

- Present State the values of the state variables for each allowed state.

- Input the input combinations allowed.

- Next-state the value of the state at time (t+1) based on the present state and the input.

- Output the value of the output as a function of the present state and (Mealy) the input.

- ✓ From the viewpoint of a truth table:

- the inputs are Input, Present State

- and the outputs are Output, Next State

#### Example 1: Alternate State Table

$$A(t+1) = A(t) \times (t) + B(t) \times (t)$$

B(t+1) =  $\overline{A}(t) \times (t)$

y(t) =  $\overline{x}(t)$  (B(t) + A(t))

| Present<br>State |   | Input       | Input State |  |

|------------------|---|-------------|-------------|--|

| A B              | x | A B         | y           |  |

| 0                | 0 | 0           |             |  |

| 0                | 0 | 1           |             |  |

| 0                | 1 | 0           |             |  |

| 0                | 1 | 1           |             |  |

| 1                | 0 | 0           |             |  |

| 1                | 0 | 1 1 1 1     |             |  |

| 1                | 1 | 0           |             |  |

| 1                | 1 | lenn1 of th |             |  |

The time sequence of inputs, outputs, and flip-flop states can be enumerated in a state table (sometimes called transition table).

$A + = A \times + B \times$  $B + = \overline{A} \times$  $y = \overline{x} (B + A)$

| Present<br>State | Next S       | tate  | Outpu        | t            |

|------------------|--------------|-------|--------------|--------------|

|                  | <i>x</i> = 0 | x = 1 | <i>x</i> = 0 | <i>x</i> = 1 |

| AB               | AB           | AB    | у            | у            |

| 00               | 00           | 01    | 0            | 0            |

| 01               | 00           | 11    | deing 1 puls | 0            |

| 10               | 00           | 10    | 1            | 0            |

| 11               | 00           | 10    | 1            | 0            |

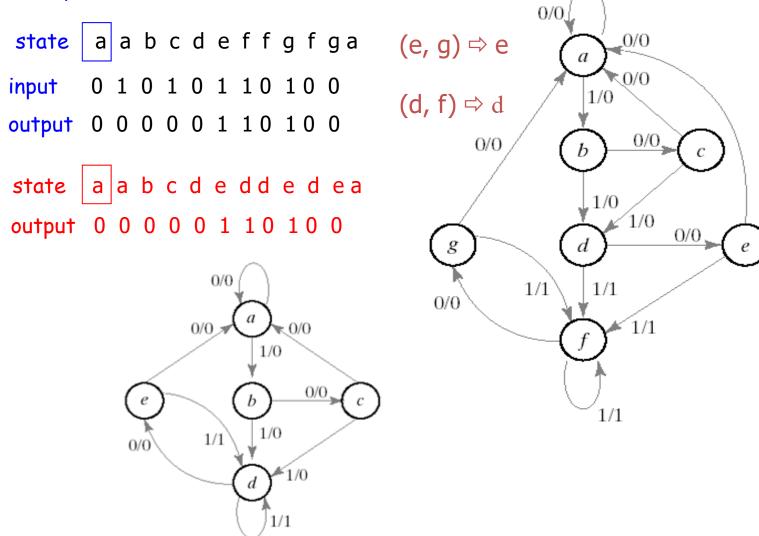

### State Diagrams

- ✓ The sequential circuit function can be represented in graphical form as a state diagram with the following components:

- A circle with the state name in it for each state

- A directed arc from the Present State to the Next State for each state transition

- A label on each directed arc with the Input values which causes the state transition, and

- A label:

- On each circle with the output value produced:

Moore type

#### <u>or</u>

On each directed arc with the output value produced: Mealy type.

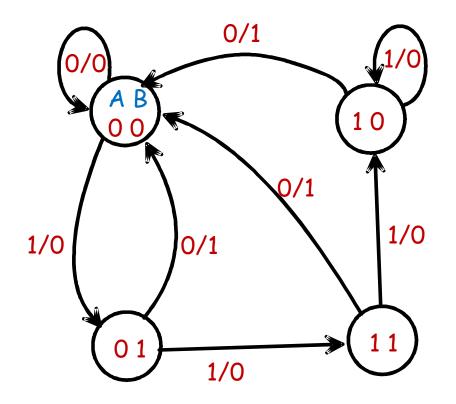

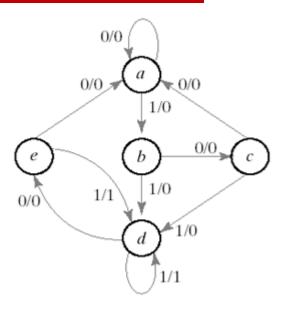

#### Example 1: State Diagram

- ✓ Diagram gets confusing for large circuits

- ✓ For small circuits, usually easier to understand than the state table

$$A + = A \times + B \times B + = \overline{A} \times A \times A$$

$$Y = \overline{X} (B + A)$$

| Present<br>State | Next         | State | Output       |       |  |

|------------------|--------------|-------|--------------|-------|--|

|                  | <i>x</i> = 0 | x = 1 | <i>x</i> = 0 | x = 1 |  |

| AB               | AB           | AB    | у            | у     |  |

| 00               | 00           | 01    | 0            | 0     |  |

| 01               | 00           | 11    | Sainel puls  | 0     |  |

| 10               | 00           | 10    | 1            | 0     |  |

| 11               | 00           | 10    | 1            | 0     |  |

1/0 : means input x = 1

output y = 0

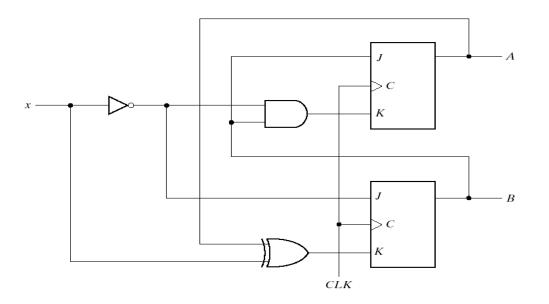

# Analysis with JK Flip-Flops

$$J_{A} = B \qquad K_{A} = B \overline{x}$$

$$J_{B} = \overline{x} \qquad K_{B} = \overline{A} \times + A \overline{x} = A \oplus x$$

Moore

8

# Analysis with JK Flip-Flop

✓ The circuit can be specified by the flip-flop input equations:

$$J_{A} = B \qquad K_{A} = B \overline{X}$$

$$J_{B} = \overline{X} \qquad K_{B} = \overline{A} \times + A \overline{X} = A \oplus X$$

| Present<br>State |        | Input         | Input State |   | all and and free | Flip-Flop<br>Inputs |    |    |   |

|------------------|--------|---------------|-------------|---|------------------|---------------------|----|----|---|

| A                | В      | x             | A           | В | topoli ipir s    | JA                  | KA | JB | K |

| 0                | 0      | 0             |             |   | the state of     |                     |    |    |   |

| 0                | 0      | 1             |             |   | CLA SECTION      |                     |    |    |   |

| 0                | 1 1 De | 0             |             |   | shion the d      |                     |    |    |   |

| 0                | 1      | A CONTRACT    |             |   | densburge        |                     |    |    |   |

| 1                | 0      | 0             |             |   | State Bark       |                     |    |    |   |

| 1                | 0      | petterl magos |             |   | The output       |                     |    |    |   |

| 1                | 1      | 0             |             |   |                  |                     |    |    |   |

| 1                | 1      | 1             |             |   |                  |                     |    |    |   |

# Analysis with JK Flip-Flops

$$A + = J\overline{A} + \overline{K}A$$

$J_A = B$  $K_A = B \overline{X}$  $B + = J\overline{B} + \overline{K}B$  $J_B = \overline{X}$  $K_B = \overline{A} \times + A \overline{X} = A \oplus X$

✓ Substituting the values of  $J_A$  and  $K_A$  from the input equations, we obtain the state equation for A:

$A = B\overline{A} + (\overline{B\overline{x}})A = \overline{A}B + A\overline{B} + Ax$

✓ The state equation provides the bit values for the column under next state of A in the state table. Similarly, the state equation for flip-flop B can be derived from the characteristic equation by substituting the values of  $J_B$  and  $K_B$ :

$$\mathsf{B} = \overline{\mathsf{x}}\overline{\mathsf{B}} + (\overline{\mathsf{A} \oplus \mathsf{x}})\mathsf{B} = \overline{\mathsf{B}}\overline{\mathsf{x}} + \mathsf{A}\mathsf{B}\mathsf{x} + \overline{\mathsf{A}}\mathsf{B}\overline{\mathsf{x}}$$

# Analysis with JK Flip-Flops

The state diagram of the sequential circuit is:  $A = B\overline{A} + (\overline{B\overline{X}})A = \overline{A}B + A\overline{B} + A\overline{X}$

$\mathsf{B} = \overline{\mathsf{x}}\overline{\mathsf{B}} + (\overline{\mathsf{A} \oplus \mathsf{x}})\mathsf{B} = \overline{\mathsf{B}}\overline{\mathsf{x}} + \mathsf{A}\mathsf{B}\mathsf{x} + \overline{\mathsf{A}}\mathsf{B}\overline{\mathsf{x}}$

| Present<br>State |       |                |   | Next<br>State |  |  |

|------------------|-------|----------------|---|---------------|--|--|

| A                | В     | x              | A | В             |  |  |

| 0                | 0     | 0              |   |               |  |  |

| 0                | 0     | 1              |   |               |  |  |

| 0                | 1 mbc | 0              |   |               |  |  |

| 0                | 1 1   | a contrational |   |               |  |  |

| 1                | 0     | 0              |   |               |  |  |

| 1                | 0     | petter I mago  |   |               |  |  |

| 1                | 1     | 0              |   |               |  |  |

| 1                | 1     | 1              |   |               |  |  |

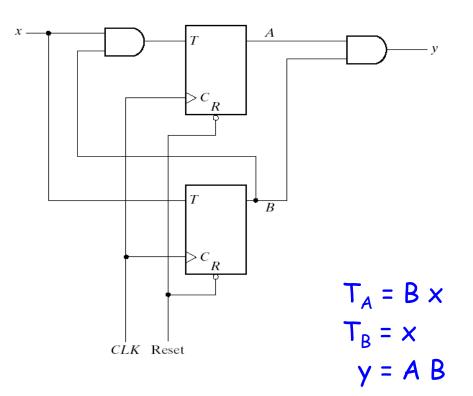

# Analysis With T Flip-Flops

✓ Characteristic equation:

Q = T⊕ Q

Moore

# Analysis With T Flip-Flops

Consider the previous sequential circuit. It has two flip-flops A and B, one input x, and one output y. It can be described algebraically by two input equations and an output equation:

$T_{A} = B \times$  $T_{B} = \times$ y = A B $A = (\overline{Bx})A + (Bx)\overline{A}$  $= A\overline{B} + A\overline{x} + \overline{A}B \times$  $B = x \oplus B$

| Present<br>State |   | Input            | 1.00 | Next<br>State |             | Output |

|------------------|---|------------------|------|---------------|-------------|--------|

| A                | B | LCXCU            | A    | B             | <b>D</b> EQ | y      |

| 0                | 0 | 0                | 195  |               | Siles       | 1      |

| 0                | 0 | 1                |      |               |             |        |

| 0                | 1 | 0                |      |               |             |        |

| 0                | 1 | nasio oli enuru  |      |               |             |        |

| 1                | 0 | 0                |      |               |             |        |

| 1                | 0 | as see 1 mini of |      |               |             |        |

| 1                | 1 | 0                |      |               |             |        |

| 1                | 1 | 1                |      |               |             |        |

# Analysis With T Flip-Flops

✓ Characteristic equation:

Q(t + 1) = T ⊕ Q

| Present<br>State |   |                   |   | ate | Output  |

|------------------|---|-------------------|---|-----|---------|

| A                | B | LCXCU             | A | B   | TR SE   |

| 0                | 0 | 0                 | 0 | 0   | 0       |

| 0                | 0 | 1                 | 0 | 1   | 0       |

| 0                | 1 | 0                 | 0 | 1   | 0       |

| 0                | 1 | unsin of onurin   | 1 | 0   | 0       |

| 1                | 0 | 0                 | 1 | 0   | 0       |

| 1                | 0 | as see 1 anial ci | 1 | 1   | 0       |

| 1                | 1 | 0                 | 1 | 1   | pollepo |

| 1                | 1 | 1                 | 0 | 0   | 1       |

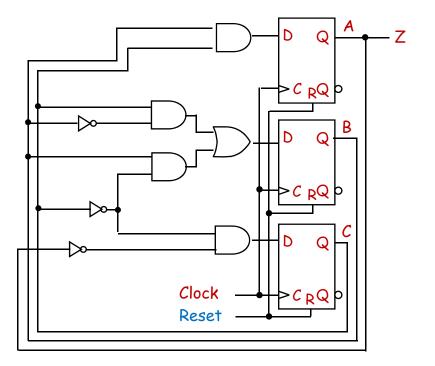

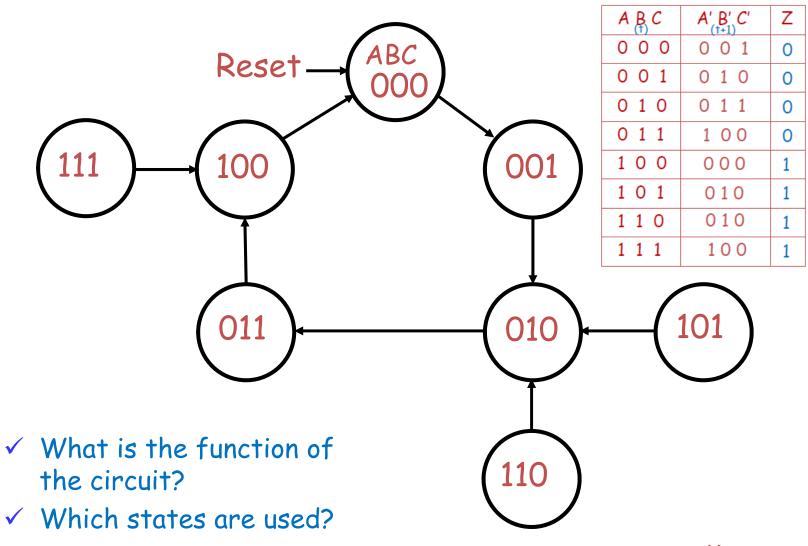

Sequential Circuit Analysis

$\checkmark$  Initialization: reset to (0, 0, 0)

✓ Equations:

A = B C

B = B C + B C

C = A C

Moore

### Example 2: State Table

|                                                 | ABC   | $A'_{(++1)}B'_{(++1)}C'$ | Ζ |

|-------------------------------------------------|-------|--------------------------|---|

|                                                 | 000   | 001                      | 0 |

| A = D C                                         | 001   | 010                      | 0 |

| $A = B C$ $B = \overline{B} C + B \overline{C}$ | 010   | 011                      | 0 |

| $C = \overline{A} \overline{C}$                 | 011   | 100                      | 0 |

|                                                 | 100   | 000                      | 1 |

| Z = A                                           | 101   | 010                      | 1 |

|                                                 | 1 1 0 | 010                      | 1 |

|                                                 | 1 1 1 | 100                      | 1 |

#### Example 2: State Diagram

Moore

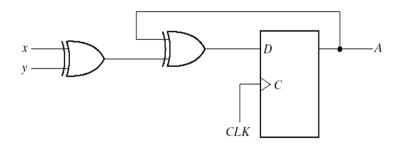

# Analysis with D Flip-Flop

✓ The circuit we want to analyze is described by the input equation

$\mathsf{D}_{\mathsf{A}} = \mathsf{A} \oplus \mathsf{X} \oplus \mathsf{Y}$

✓ The D<sub>A</sub> symbol implies a D flip-flop with output A. The x and y variables are the inputs to the circuit. No output equations are given, so the output is implied to come from the output of the flip-flop.

Moore

# Analysis with D Flip-Flop

The binary numbers under A x y are listed from 000 through 111.

The next state values are obtained from the state equation

$$\mathsf{D}_{\mathsf{A}} = \mathsf{A} \oplus \mathsf{X} \oplus \mathsf{Y}$$

$\checkmark$  The state diagram consists of two circles-one for each state

| Present<br>state | Inputs  | Next<br>state |

|------------------|---------|---------------|

| Α                | хy      | Α             |

| 0                | 0 0     |               |

| 0                | 0 1     |               |

| 0                | 1 0     |               |

| 0                | 1 1     |               |

| 1                | 0 0     |               |

| 1                | $0 \ 1$ |               |

| 1                | 1 0     |               |

| 1                | 1 1     |               |

### Equivalent State Definitions

- Two states are equivalent if their response for each possible input sequence is an identical output sequence.

- Alternatively, two states are equivalent if their outputs produced for each input symbol is identical and their next states for each input symbol are the same or equivalent.

- Two states that are not equivalent are distinguishable

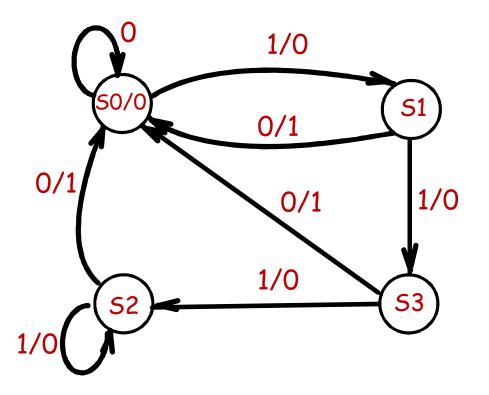

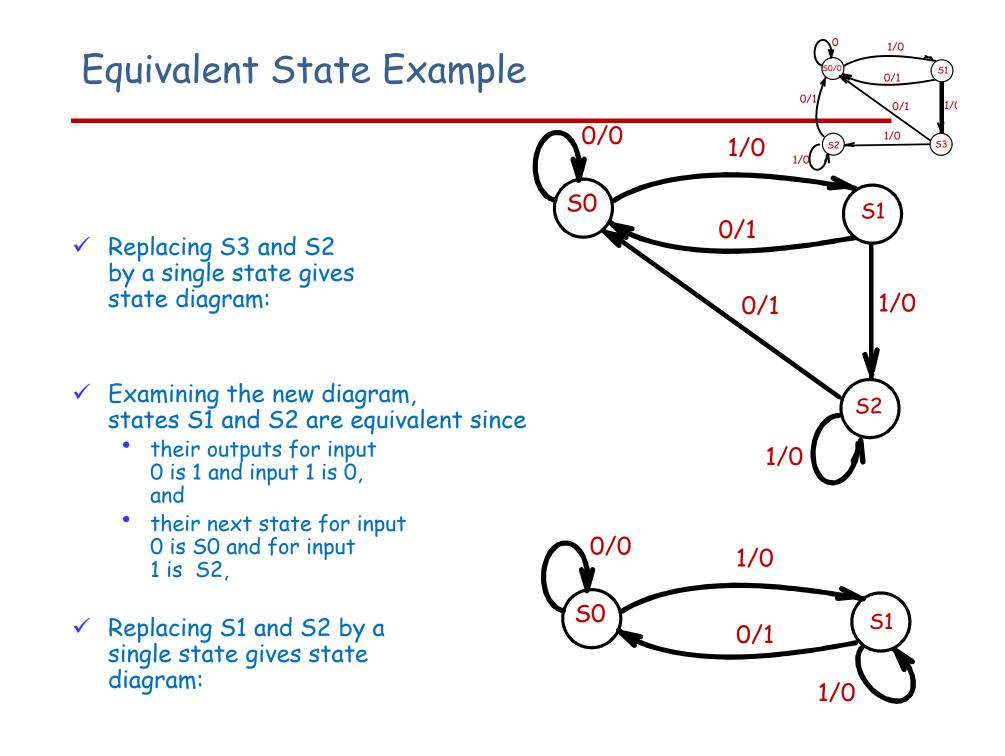

### Equivalent State Example

✓ For states S3 and S2,

- the output for input 0 is 1 and input 1 is 0, and

- the next state for input 0 is S0 and for input 1 is S2.

- states S3 and S2 are equivalent.

### Moore and Mealy Models

- Sequential Circuits or Sequential Machines are also called Finite State Machines (FSMs).

- ✓ Two formal models exist:

- Moore Model

- Named after E.F. Moore

- Outputs are a function ONLY of states

- Usually specified on the states.

Mealy Model

- Named after G. H. Mealy

- Outputs are a function of inputs AND states

- Usually specified on the state transition arcs.

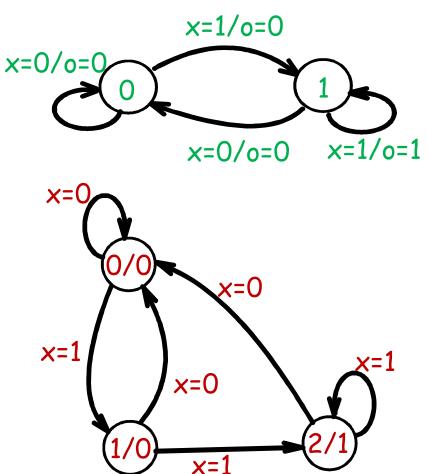

### Moore and Mealy Example Diagrams & Tables

Mealy Model State Diagram maps inputs and state to outputs

| Present | Next       | State | Out | put |

|---------|------------|-------|-----|-----|

| State   | <b>x=0</b> | ×=1   | x=0 | x=1 |

| 0       | 0          | 1     | 0   | 0   |

| 1       | 0          | 1     | 0   | 1   |

Moore Model State Diagram maps states to outputs

| Present | Next | State | Output |

|---------|------|-------|--------|

| State   | x=0  | x=1   |        |

| 0       | 0    | 1     | 0      |

| 1       | 0    | 2     | 0      |

| 2       | 0    | 2     | 1      |

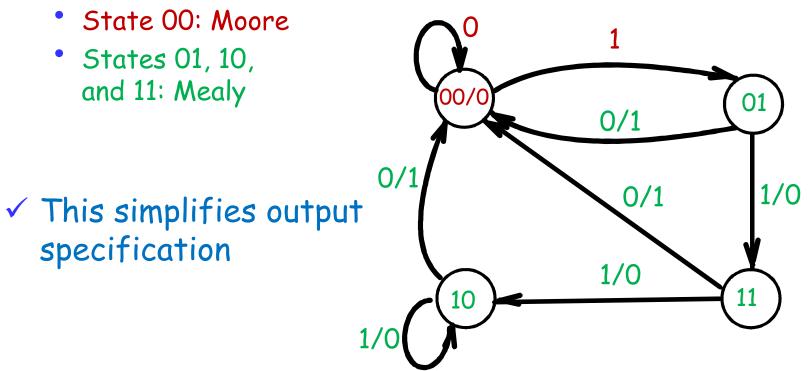

### Mixed Moore and Mealy Outputs

- ✓ In real designs, some outputs may be Moore type and other outputs may be Mealy type.

- Example: Figure can be modified to illustrate this

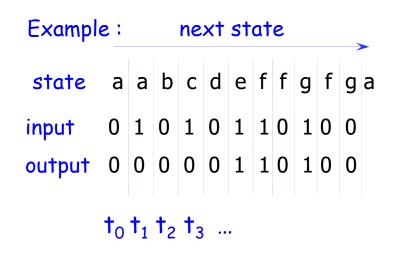

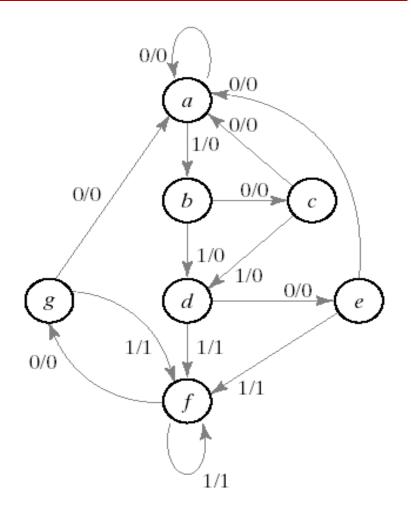

We now proceed to reduce the number of states for this example. First, we need the state table; it is more convenient to apply procedures for state reduction using a table rather than a diagram. The state table of the circuit is listed in Table 5-6 and is obtained directly from the state diagram.

|               | Next         | State        | Out          | put          |

|---------------|--------------|--------------|--------------|--------------|

| Present State | <i>x</i> = 0 | <i>x</i> = 1 | <i>x</i> = 0 | <i>x</i> = 1 |

| a             | a            | Ь            | 0            | 0            |

| b             | с            | d            | 0            | 0            |

| c             | а            | d            | 0            | 0            |

| d             | e            | f            | 0            | 1            |

| e             | a            | f            | 0            | 1            |

| f             | g            | f            | 0            | 1            |

| 8             | a            | f            | 0            | 1            |

States g and e are two such states: they both go to states a and f and have outputs of 0 and 1 for x=0 and x=1, respectively. Therefore, states g and e are equivalent and one of these states can be removed. The procedure of removing a state and replacing it by its equivalent is demonstrated in Table 5-7. The row with present g is removed and state g is replaced by state e each time it occurs in the next-state columns.

| Present State | Next State   |              | Output              |              |  |

|---------------|--------------|--------------|---------------------|--------------|--|

|               | <i>x</i> = 0 | <i>x</i> = 1 | <i>x</i> = <b>0</b> | <i>x</i> = 1 |  |

| а             | а            | Ь            | 0                   | 0            |  |

| b             | с            | d            | 0                   | 0            |  |

| С             | а            | d            | 0                   | 0            |  |

| d             | e            | f            | 0                   | 1            |  |

| e             | а            | f            | 0                   | 1            |  |

| f             | e            | f            | 0                   | 1            |  |

Present state f now has next states e and f and outputs 0 and 1 for x=0 and x=1, respectively. The same next states and outputs appear in the row with present state d. Therefore, states f and d are equivalent and state f can be removed and replaced by d. The final reduced table is shown in Table 5-8. The state diagram for the reduced table consists of only five states.

| Present State       | Next State          |              | Output       |              |  |

|---------------------|---------------------|--------------|--------------|--------------|--|

|                     | <b>x</b> = <b>0</b> | <i>x</i> = 1 | <i>x</i> = 0 | <i>x</i> = 1 |  |

| a                   | a                   | Ь            | 0            | 0            |  |

| Ь                   | с                   | d            | 0            | 0            |  |

| physical co 2 conen | a                   | d            | 0            | 0            |  |

| diam dia            | e                   | d            | 0            | 1            |  |

| e                   | а                   | d            | 0            | 1            |  |

29

Example :

# State Assignment

Table 5 10

| Table 5-9           Three Possible Binary State Assignments |                            |                               |                         |  |

|-------------------------------------------------------------|----------------------------|-------------------------------|-------------------------|--|

| State                                                       | Assignment 1<br>Binary pse | Assignment 2<br>udo Gray code | Assignment 3<br>One-hot |  |

| a                                                           | 000                        | 000                           | 00001                   |  |

| b                                                           | 001                        | 001                           | 00010                   |  |

| с                                                           | 010                        | 011                           | 00100                   |  |

| d                                                           | 011                        | 010                           | 01000                   |  |

| е                                                           | 100                        | 110                           | 10000                   |  |

| Present State | Next State   |              |      | Output       |       |

|---------------|--------------|--------------|------|--------------|-------|

|               | <i>x</i> = 0 | <i>x</i> = 1 | in L | <i>x</i> = 0 | x = 1 |

| 000           | 000          | 001          | B    | 0            | 0     |

| 001           | 010          | 011          |      | 0            | 0     |

| 010           | 000          | 011          |      | 0            | 0     |

| 011           | 100          | 011          |      | 0            | 1     |

| 100           | 000          | 011          |      | 0            | 1     |